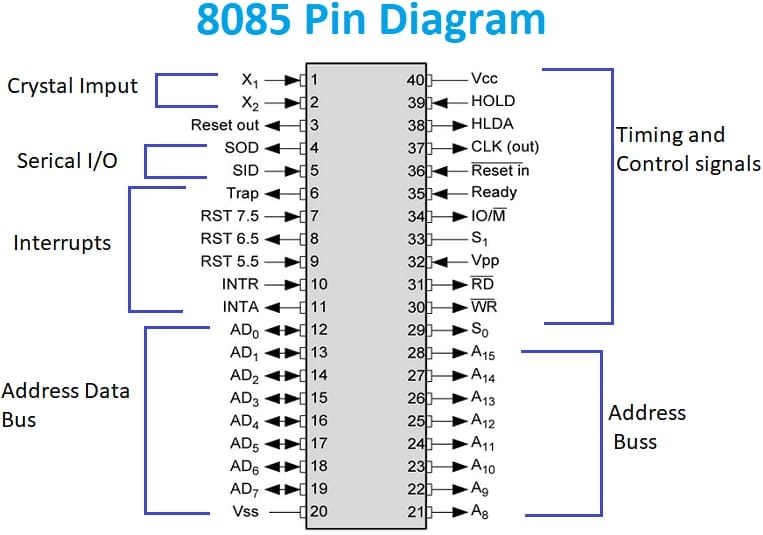

In that program, we shall study the Pin Diagram of 8085 Microprocessor and their description.

What is the 8085 Microprocessor Pin Diagram?

The 8085 pin diagram includes 40 pins of the microprocessor. The pins could be categorized into six groups-address and data bus, get a handle on signals, position signals, power supply, and serial input/output ports.

8085 Pin Diagram in Microprocessor

X1 AND X2

Here is the first flag in the 8085 Flag Plan in Microprocessor. The x1 and x2 represent the crystal oscillator that will give volume for the microprocessor.

Address Bus (A8-A15)

Here is the 2nd flag in the 8085 Flag Plan in Microprocessor. The handle bus pins vary from A8 to A15 and these pins do the information move only.

Address Bus (or) Data Bus (AD0-AD7)

Here is the next flag in the 8085 Flag Plan in Microprocessor. The handle bus pins or data bus pins vary from AD0 to AD7, and these pins are named multiplexing lines that will do both handles as well as data transfer.

Address Latch Enable (ALE)

Here is the 4th flag in the 8085 Flag Plan in Microprocessor. It’s an energetic large signal. It presents the position of data lines (AD0-AD7). If the value is good then it shows that the handle is going in the lines and if the value is negative then data is traveling in the lines.

Status Signal (IO/M)

Here is the fifth flag in the 8085 Flag Plan in Microprocessor. It shows people whether the handle is supposed for storage or input/output. In the event once we get a confident indicate it presents that individuals ‘ve got i/o read or i/o create and once we get a poor indicate it presents storage activation.

Status Signals (S0-S1)

Here is the 6th flag in the 8085 Flag Plan in Microprocessor. The position signals S0, and S1 give various functions as well as position based on their status.

- 01 then a operation is going to be HALT.

- 10 then a operation is going to be WRITE

- 10 then a operation is going to be READ

- 11 then a operation is going to be FETCH

RD

Here is the 7th flag in the 8085 Flag Plan in Microprocessor. The RD is an energetic reduced indicate and it is employed for controlling the microprocessor READ operation. Once the RD flag moves small then the 8085 microprocessor knows the data from the I/O product or memory.

WR

Here is the 8th flag in the 8085 Flag Plan in Microprocessor. It’s the power to manage the microprocessor’s create operations. Once the WR flag moves small the information is going to be published to the I/O product or memory.

READY

Here is the 9th flag in the 8085 Flag Plan in Microprocessor. The READY flag is for ensuring whether a device is set for taking or moving data. Once the flag is large the device is ready for move, if it is perhaps not then a microprocessor stays till that flag moves high.

HOLD

Here is the 10th flag in the 8085 Flag Plan in Microprocessor. The HOLD flag specifies when any product is challenging the usage of an handle as well as a data bus.

HLDA

Here is the 11th flag in the 8085 Flag Plan in Microprocessor. It’s the response indicate of HOLD and is employed to establish whether that indicate is acquired or not. This indicate should go reduced after the implementation of HOLD demand.

INTR

Here is the 12th flag in the 8085 Flag Plan in Microprocessor. This really is an stop indicate, and the priority with this among the interrupts is low. This indicate could be permitted or banned by the software. The 8085 microprocessor finishes the training that is being performed when the INTR flag moves large and understands the INTR indicate and progresses it.

INTA

Here is the 13th flag in the 8085 Flag Plan in Microprocessor. INTA represents stop acknowledgement. When an stop indicate comes, then it ought to be acknowledged by INTA. It is an active-low indicate that’s for zero it will method and for one it won’t.

RST 5.5, RST 6.5, RST 7.5

Here is the 14th flag in the 8085 Flag Plan in Microprocessor. They’re the restart maskable interrupts or Vectored Stops which are employed for the insertion of an interior restart function repeatedly. All these interrupts are maskable.

TRAP

Here is the 15th flag in the 8085 Flag Plan in Microprocessor. TRAP is really a non-maskable stop, and it does not let or end a program. TRAP has maximum precedence between interrupts. The priority buy is TRAP, RST 5.5, RST 6.5, RST 7.5, and INTR.

RESET IN

Here is the 16th flag in the 8085 Flag Plan in Microprocessor. It’s used to reset the program counter toward zero. Additionally, it rearranges stop allow as well as HLDA flip-flops (FFs).

RST (RESET) OUT

Here is the 17th flag in the 8085 Flag Plan in Microprocessor. It’ll reset all of the units linked to the microprocessor.

X1 X2

Here is the 18th flag in the 8085 Flag Plan in Microprocessor. X1, and X2 terminals which are connected with the surface oscillator for generating the mandatory as well as suitable operation of a clock.

CLK

Here is the 19th flag in the 8085 Flag Plan in Microprocessor. Often CLK indicate must be made from microprocessors that can be used in favour of other peripherals or else other digital incorporated circuits. This really is provided with a CLK pin.

SID and SOD

Here is the 30th flag in the 8085 Flag Plan in Microprocessor. These two pins are employed for serial data communication. In the serial input data, the data is uploaded in to the 7th little the accumulator while RIM training is performed. RIM(Read stop mask) verifies whether the stop is protected or perhaps not covered. In the serial o/p data the result of the information is sent toward the 7th little the accumulator when an training of SIM is performed.

VSS and VCC

Here is the 31st flag in the 8085 Flag Plan in Microprocessor. VSS is a ground flag while Vcc is really a +5v pin.